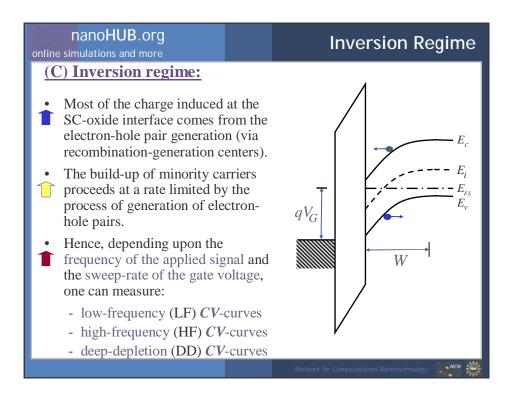

### Regions of operation

- Regions of operation for MOS capacitor with *p*-type SC:

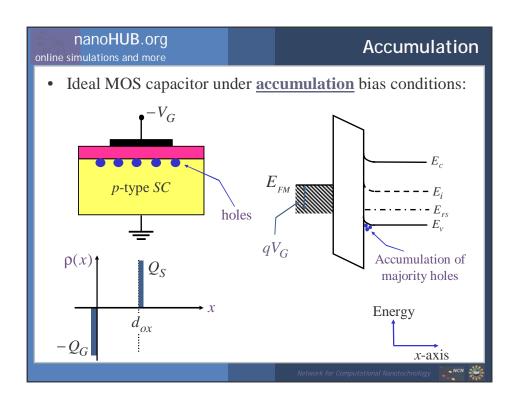

- (a) accumulation:  $\varphi_s < 0$

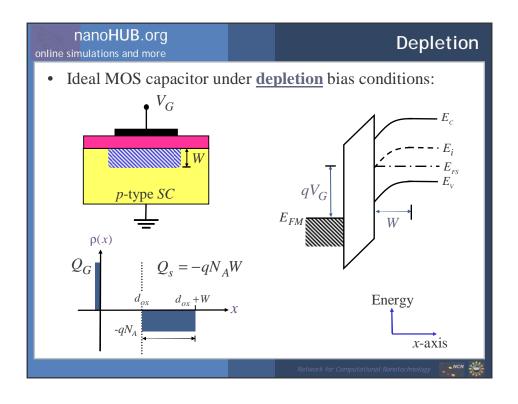

- (b) depletion:  $0 < \varphi_s < 2\varphi_F$

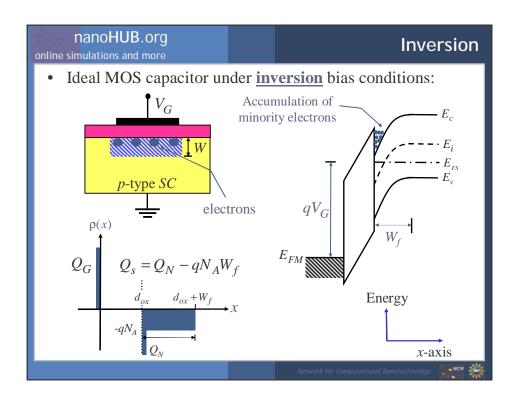

- (c) inversion:  $\varphi_s \ge 2\varphi_F$

- The condition  $\phi_s=2 \phi_F$  is called **onset of inversion**:

$$\begin{aligned} n_s &= n_i \exp\left[\frac{E_{FS} - E_i(0)}{k_B T}\right] = n_i \exp\left(\frac{q \varphi_F}{k_B T}\right) \\ p_s &= n_i \exp\left[\frac{E_i(0) - E_{FS}}{k_B T}\right] = n_i \exp\left(-\frac{q \varphi_F}{k_B T}\right) \end{aligned} \rightarrow \begin{cases} n_s &= p(bulk) \\ n_s p_s &= n_i^2 \end{cases}$$

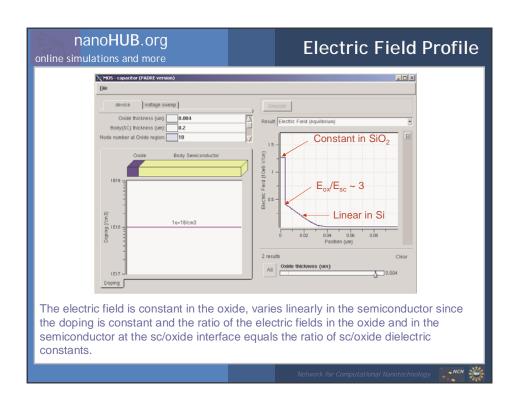

# nanoHUB.org online simulations and more $\frac{K_1 \epsilon_0}{k_2 \epsilon_0} \xrightarrow{F_{t1}} \frac{K_1 \epsilon_0}{F_{t2}} \xrightarrow{F_{t2}} F_{t2}$ $F_{t1} = F_{t2}$ • Electric field profile for a MOS capacitor with p-type SC under depletion condition: $\frac{F_{t1}}{F_{t2}} = \frac{F_{t2}}{F_{t2}}$ • Mostwark for Computational Nanotechnology

# nanoHUB.org 2. MOS Capacitor Electrostatics

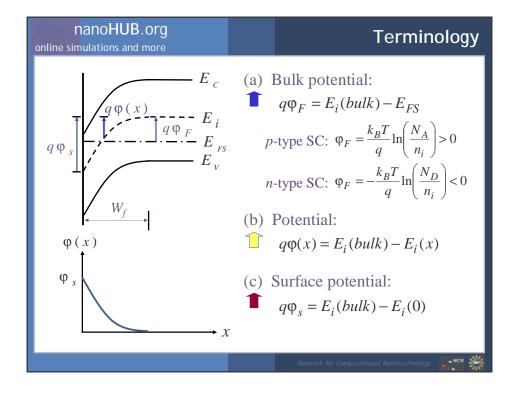

• The potential distribution (profile) in the semiconductor side of a MOS capacitor is described with the 1D Poisson equation:  $\frac{d^2}{dt} = O(r)$

$\frac{d^2\varphi}{dx^2} = -\frac{\rho(x)}{k_s \varepsilon_0}$

where the space charge density is given by:

$$\rho(x) = q \left( p - n + N_D^+ - N_A^- \right)$$

- The 1D Poisson equation can be solved using one of the following approaches:

- (1) Delta-depletion approximation

- (2) Exact analytical model

- (3) Using numerical solution techniques

### A. Delta-Depletion Approximation

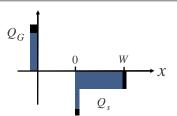

- Accumulation charge is replaced with a delta-charge positioned right at the semiconductor interface.

- The electric field and the electrostatic potential are:

$$F(x) = \varphi(x) = 0$$

for  $x > 0$

- The charge associated with the minority carriers resides in an extremely narrow region at the SC/oxide interface.

- To first order we can assume that:

$$\varphi_s = 2\varphi_F \quad \text{for} \quad V_G > V_{th}$$

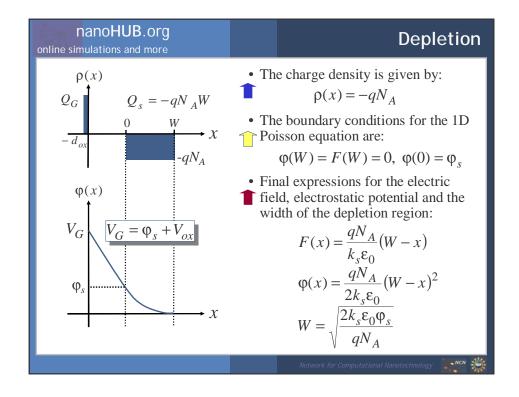

### Depletion, Cont'd

online simulations and more

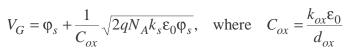

The surface potential is an internal parameter. We therefore need to relate  $\varphi_s$  to the gate voltage  $V_G$  using:

$$V_G = V_{ox} + \varphi_s = F_{ox} d_{ox} + \varphi_s$$

where:

$$F_{ox} = \frac{k_s}{k_{ox}} F_s = \frac{k_s}{k_{ox}} \frac{q N_A W}{k_s \varepsilon_0} = \frac{q N_A W}{k_{ox} \varepsilon_0}$$

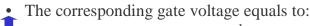

• Final expression for the  $V_G$ - $\varphi_s$  relationship:

• Threshold voltage definition:

## nanoHUB.org

### Depletion, Cont'd

• Graphical representation of the  $V_G$ - $\varphi_s$  relationship:

- Surface potential varies rapidly with  $V_G$  when the device is **depletion biased**. Gate voltage is divided proportionally between the semiconductor and the oxide.

- When the semiconductor is accumulated or inverted, it takes large  $V_G$  to produce small change in  $\varphi_s$ . Changes in the applied bias are almost all dropped across the oxide.

online simulations and more

### B. Exact Analytical Model

To solve for the electrostatic potential and the electric field profile under arbitrary bias conditions, one needs to go beyond the delta-depletion approximation and use the exact expression for the charge density  $\rho(x)$  in the 1D Poisson equation:

$$\rho(x) = q(p - n + N_D - N_A)$$

=  $q(p_{po}e^{-\phi/V_T} - n_{po}e^{\phi/V_T} + N_D - N_A)$

• Analytical tricks that we need to use to get to the answer:

(1)

$$\frac{d^2 \varphi}{dx^2} = \frac{d}{dx} \left( \frac{d\varphi}{dx} \right) = \frac{d}{d\varphi} \left( \frac{d\varphi}{dx} \right) \frac{d\varphi}{dx} = \frac{u du}{d\varphi}, \quad u = \frac{d\varphi}{dx} = -F(x)$$

(2)  $\rho(x) = 0$  in the semiconductor bulk, where  $\varphi = 0$ .

### etwork for Computational Nanotechnology

### nanoHUB.org

### Exact Analytical Model, Cont'd

Integrating the 1D Poisson equation from the bulk up to some point at a distance x from the SC/oxide interface (at which point the potential is  $\varphi$ ) we get:

$$F^{2}(\varphi) = \frac{2qp_{po}V_{T}}{k_{s}\varepsilon_{0}} \left[ \left( e^{-\varphi/V_{T}} + \frac{\varphi}{V_{T}} - 1 \right) + \frac{n_{po}}{p_{po}} \left( e^{\varphi/V_{T}} - \frac{\varphi}{V_{T}} - 1 \right) \right]$$

Now, introducing the extrinsic *Debye* length  $L_D$ , we can write:

$$L_D = \sqrt{\frac{k_s \varepsilon_0 V_T}{q p_{po}}} \to F(\varphi) = \pm \frac{\sqrt{2} V_T}{L_D} f(\varphi)$$

- (+) sign is for positive  $\varphi$

- (-) sign is for negative φ

### Exact Analytical Model, Cont'd

- At the SC/oxide interface we have  $\varphi = \varphi_s$ , which leads to the following results for:

- (a) electric field:  $F_s = F(\varphi_s) = \pm \sqrt{2}V_T f(\varphi_s)/L_D$

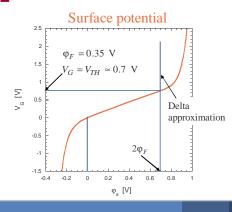

- (b) total sheet-charge density:

$$Q_s = -k_s \varepsilon_0 F_s$$

$$= \mp \frac{\sqrt{2}k_{s}\varepsilon_{0}V_{T}}{L_{D}} \left[ \left( e^{-\varphi_{s}/V_{T}} + \frac{\varphi_{s}}{V_{T}} - 1 \right) + \frac{n_{po}}{p_{po}} \left( e^{\varphi_{s}/V_{T}} - \frac{\varphi_{s}}{V_{T}} - 1 \right) \right]$$

- $\implies$  flat-band condition:  $\varphi_s = 0 \rightarrow Q_s = 0$

- $\implies$  depletion regime:  $0 < \varphi_s < 2\varphi_F \rightarrow Q_s < 0$

- inversion regime:  $\varphi_s > 2\varphi_F \rightarrow Q_s \propto -\exp(\varphi_s / 2V_T)$

- accumulation regime:  $\varphi_s < 0 \rightarrow Q_s \propto \exp(-\varphi_s/2V_T)$

Network for Computational Nanotechnology

## nanoHUB.org

### Exact Analytical Model, Cont'd

$$V_G = \varphi_s + V_{ox} = \varphi_s + \frac{k_s}{k_{ox}} F_s d_{ox}$$

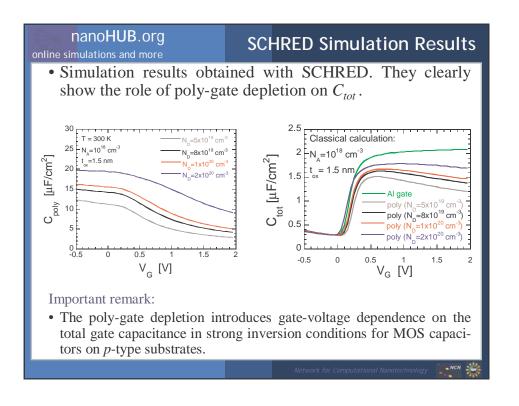

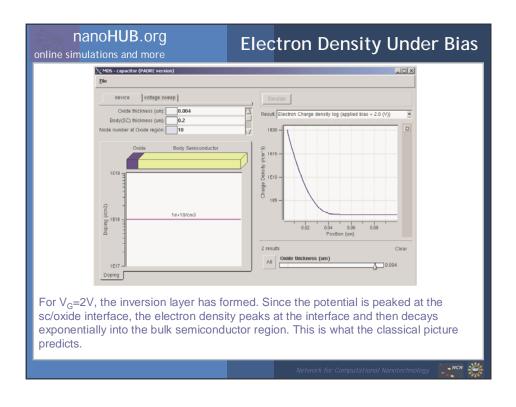

Simulation results for  $N_A=10^{16}$  cm<sup>-3</sup> and  $d_{ox}=4$  nm:

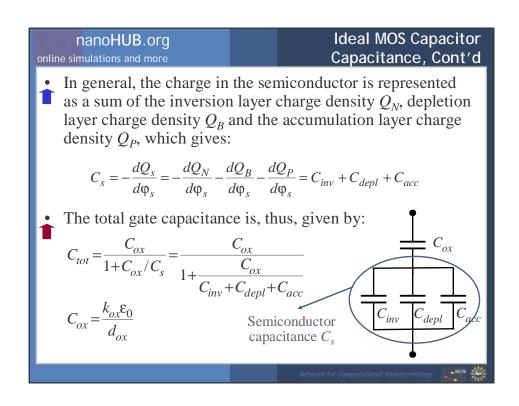

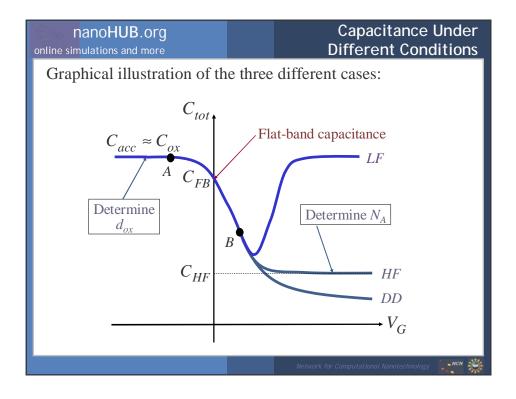

# nanoHUB.org online simulations and more 3. Ideal MOS Capacitor Capacitance • The capacitance per unit area of an MOS capacitor is calculated using: $C_{tot} = \frac{dQ_G}{dV_G} = -\frac{dQ_S}{d(V_{ox} + \varphi_S)} = \frac{1}{-\frac{dV_{ox}}{dQ_S} - \frac{d\varphi_S}{dQ_S}}$ $= \frac{1}{1/C_{ox} + 1/C_S} = \frac{C_{ox}}{1 + C_{ox}/C_S}$ where: • $C_{ox}$ is the oxide capacitance • $C_{s}$ is the SC capacitance

Ideal MOS Capacitor Capacitance - Accumulation

online simulations and more

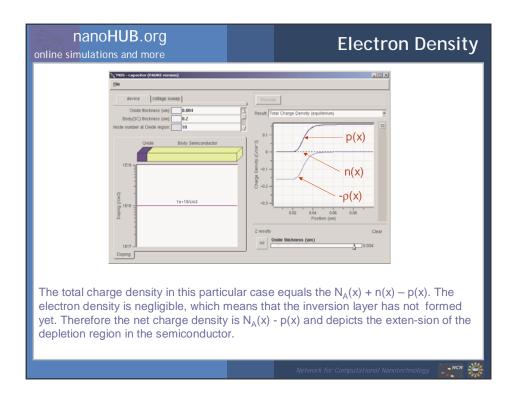

• Using the analytical model expression for the semiconductor charge per unit area  $Q_s$ , we get:

$$C_{s} = -\frac{dQ_{s}}{d\varphi_{s}} = Cso \frac{\left| 1 - e^{-\varphi_{s}/V_{T}} + \frac{n_{po}}{p_{po}} \left( e^{\varphi_{s}/V_{T}} - 1 \right) \right|}{\sqrt{2}f(\varphi_{s})}$$

$$f(\varphi_{s}) = \left[ e^{-\varphi_{s}/V_{T}} + \frac{\varphi_{s}}{V_{T}} - 1 + \frac{n_{po}}{p_{po}} \left( e^{\varphi_{s}/V_{T}} - \frac{\varphi_{s}}{V_{T}} - 1 \right) \right]^{1/2}$$

$$C_{so} = \frac{k_{s}\varepsilon_{0}}{L_{D}} \rightarrow \text{Flat-band capacitance}$$

(A) Accumulation regime:

$$\phi_s < 0 \rightarrow f(\phi_s) \propto \exp(-\phi_s / 2V_T)$$

$$dQ_N = 0, \ dQ_B = 0$$

$$\rightarrow C_{tot} \approx C_{ox}$$

The total gate capacitance is approximately equal to the oxide capacitance.

### nanoHUB.org

**Depletion Regime**

online simulations and more

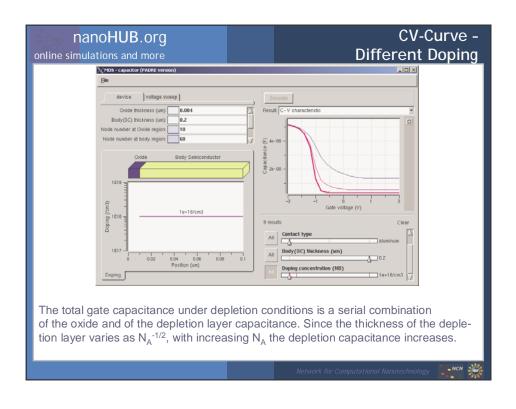

### (B) Depletion regime:

In depletion regime, the inversion charge is negligible when compared to the depletion charge. Hence:

$$\begin{array}{c} 0 < \varphi_s < 2\varphi_F \rightarrow f(\varphi_s) \propto \sqrt{\varphi_s/V_T} \\ dQ_N = 0, \ dQ_P = 0 \end{array} \right\} \rightarrow C_s = \frac{Cso}{\sqrt{2\varphi_s/V_T}} = \sqrt{\frac{k_s \varepsilon_0 q N_A}{2\varphi_s}}$$

The total capacitance is, thus, given by:

$$C_{tot} = \frac{C_{ox}}{1 + \frac{C_{ox}}{C_s}} = \frac{C_{ox}}{1 + \frac{C_{ox}}{C_{depl}}} = \frac{k_{ox} \varepsilon_0}{d_{ox} + k_{ox} \varepsilon_0 \sqrt{\frac{2\varphi_s}{k_s \varepsilon_0 q N_A}}}$$

- Important remarks:

- $\rightarrow$  If  $N_A$  increases, then  $C_{tot}$  increases.

- $\rightarrow$  If  $d_{ox}$  increases,  $C_{tot}$  decreases.

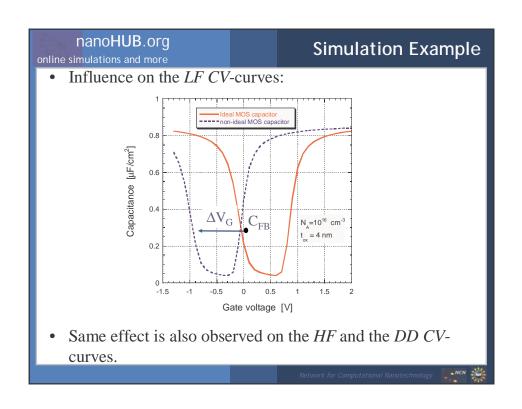

### Low-Frequency CV-curve

• AC-frequency low and sweeprate low to allow for the generation of the inversion layer

ration of the inversion layer electrons and their response to the applied AC signal.

• Inversion layer and total gate capacitance:

$$\begin{aligned}

& \left\{ \begin{array}{l} \widehat{\varphi}_s > 2\varphi_F \to f(\varphi_s) \propto \exp(\varphi_s / 2V_T) \\

& dQ_P = 0 \end{aligned} \right\} \to C_s \approx C_{inv} \approx C_{so} \sqrt{\frac{n_{po}}{2p_{po}}} e^{\varphi_s / 2V_T}

\end{aligned}$$

$$C_{tot} = \frac{C_{ox}}{1 + C_{ox}/C_s} = \frac{C_{ox}}{1 + C_{ox}/C_{inv}} \approx C_{ox}$$

The total gate capacitance is approximately equal to the oxide capacitance.

### Network for Computational Nanotechnology

### NCN 💥

### nanoHUB.org

High-Frequency CV-Curve

\*AC-frequency high, which prevents the response of the minority carriers. The sweep-rate is low, thus allowing for the generation of the inversion layer electrons.

• Depletion layer and total gate capacitance:

$$\phi_s \approx 2\phi_F \to f(\phi_s) = \sqrt{2\phi_F/V_T} \\ dQ_N = 0, \quad dQ_P = 0$$

$$\to C_s \approx C_{depl} \approx \sqrt{\frac{k_s \varepsilon_0 q N_A}{2(2\phi_F)}}$$

$$C_{tot} = \frac{C_{ox}}{1 + C_{ox}/C_{depl}} = \frac{C_{ox}}{1 + C_{ox}\sqrt{\frac{2(2\varphi_F)}{k_s \epsilon_0 q N_A}}} \approx const$$

### **Deep-Depletion CV-Curve**

• AC-frequency high, which prevents the response of the minority carriers. The sweep-rate is also high, thus preventing the generation of the inversion layer electrons.

Depletion layer and total gate capacitance:

$$\begin{cases} f(\varphi_s) = \sqrt{\varphi_s/V_T} \\ dQ_N = 0, \ dQ_P = 0 \end{cases} \rightarrow C_s \approx C_{depl} \approx \sqrt{\frac{k_s \varepsilon_0 q N_A}{2\varphi_s}}$$

$$C_{tot} = \frac{C_{ox}}{1 + \frac{C_{ox}}{C_{depl}}} = \frac{C_{ox}}{1 + C_{ox} \sqrt{\frac{2\varphi_s}{k_s \varepsilon_0 q N_A}}}$$

### nanoHUB.org

### What is Low Frequency?

• The SCR generation current density equals to:

$$J_{SCR} = q n_i W / \tau_g$$

$J_{SCR} = q n_i W / \tau_g$  While  $J_{SCR}$  flows in the semiconductor, the current flowing through the

$$J_D = C_{ox} dV / dt$$

• For the inversion charge to be able to respond, we must have that the SCR current must be able to supply the required displacement current, i.e.

$$C_{ox}dV/dt \le qn_iW/\tau_g \rightarrow dV/dt \le \frac{qn_iW}{C_{ox}\tau_g}$$

**Example:**  $d_{ox}$ =100 nm, W=1  $\mu$ m,  $C_{ox}$ =3.45×10<sup>-8</sup> F/cm<sup>2</sup>:

$\tau_e = 10 \,\mu s$ ,  $dV/dt \le 0.65 \,V/s$ ,  $f_{eff} = 45 \,Hz$  (not a severe constraint)  $\tau_{o}=1 \text{ ms}, dV/dt \le 6.5 \text{ mV/s}, f_{eff}=0.4 \text{ Hz} \text{ (severe constraint)}$

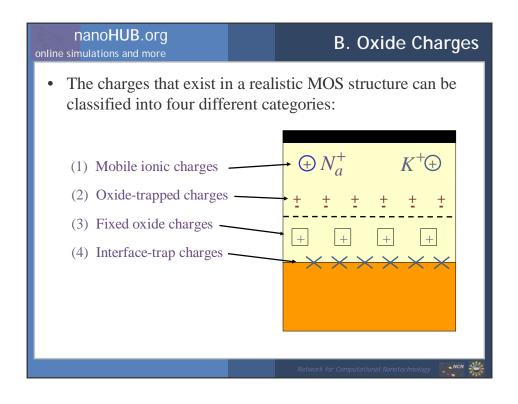

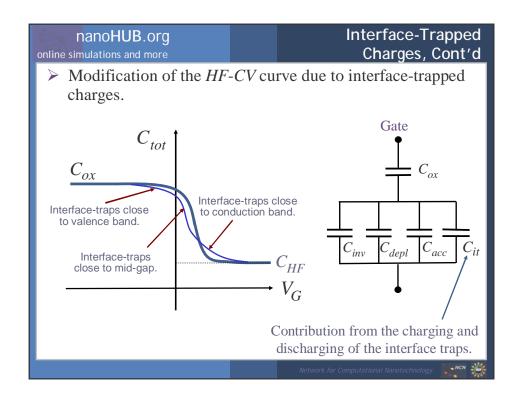

4. Deviations from the Ideal Model

There are several factors that lead to deviation of the measured *CV*-curves from what the ideal model predictions are:

- Work-function difference

- Oxide charges (interface-trap, fixed-oxide, oxide-trap and mobile oxide charges)

- Depletion of the poly-silicon gates

- Quantum-mechanical space-quantization effects

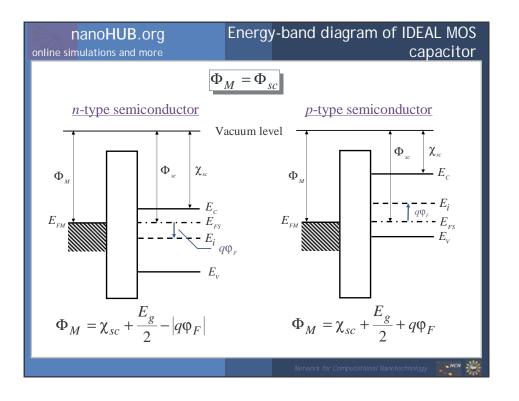

# Ideal MOS capacitor with a p-type semiconductor $\Phi_{M} = \chi_{sc} + \frac{E_{g}}{2} + q \Phi_{F}$ Real MOS capacitor with a p-type semiconductor $\Phi_{M} = \chi_{sc} + \frac{E_{g}}{2} + q \Phi_{F}$

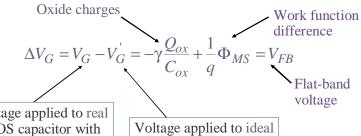

# nanoHUB.org online simulations and more The flat-band voltage $V_{FB}$ equals the required gate voltage to achieve flat-band conditions. The workfunction difference modifies the relationship between the surface potential and the applied bias. This gives rise to threshold voltage shift between the ideal and real CV-curves: $\Delta V_G = V_G - V_G' = \frac{1}{q} \Phi_{MS} = \frac{1}{q} (\Phi_M - \Phi_{SC})$ Voltage applied to real MOS capacitor Voltage applied to ideal MOS capacitor

### Oxide Charges, Cont'd

- The expression for the voltage drop across the oxide layer  $V_{ox}$  in the presence of a non-zero charge distribution  $\rho(x)$  is found from the solution of the 1D Poisson equation, using the boundary conditions:  $\varphi_{ox}(0)=0$  and  $\varphi_{ox}(d_{ox})=V_{ox}$ .

- The final result of this calculation is given below:

$$V_{ox} = d_{ox}F_{ox}(d_{ox}) - \gamma \frac{Q_{ox}}{C_{ox}}, \quad \gamma = \frac{1}{d_{ox}} \frac{\int_{0}^{d_{ox}} x \rho_{ox}(x) dx}{\int_{0}^{d_{ox}} \rho_{ox}(x) dx}$$

- Special cases:

- **1** uniform charge distribution:  $\gamma=1/2$

- **2** Charges at the SC/oxide interface:  $\gamma=1$

- 3 Charges at the metal/oxide interface:  $\gamma=0$

### nanoHUB.org

### Oxide Charges, Cont'd

The threshold voltage shift due to workfunction difference and charges in the oxide is given by:

Voltage applied to real MOS capacitor with oxide charges

MOS capacitor

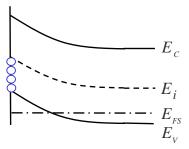

• Important note: All the charges (mobile ion charges, fixed oxide charges, oxide trapped charges) except the interfacetrap charges lead to rigid shift of the CV curve.

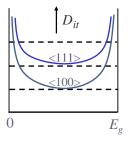

### **Interface-Trapped Charges**

- More information on interface-trapped charges:

- ➤ Most of the interface-trapped charges can be neutralized by low-temperature hydrogen annealing.

- > The interface trap density is given by:

$$D_{it} = \frac{1}{q} \frac{dQ_{it}}{dE} \left( \frac{\text{\# of charges}}{cm^2 eV} \right)$$

- ➤ Interface trap charges can be:

- acceptor-like (above the intrinsic level)

- donor-like (below the intrinsic level)

work for Computational Nanotechnology

# nanoHUB.org

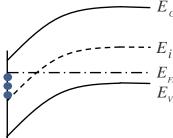

# Interface-Trapped Charges, Cont'd

➤ Use simplified model that all of the states below the Fermi level are full and all of the states above the Fermi level are empty.

**Depletion:**

The excess negative charges lead to positive shift.

### **Accumulation:**

The excess positive charges lead to negative shift.

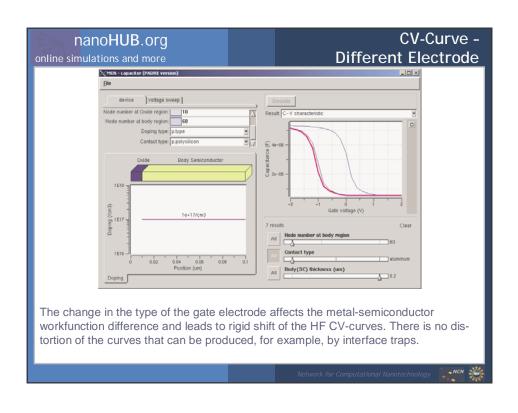

# nanoHUB.org Example 2: Workfunction Difference, Doping Dependence (PADRE simulation)

### **Problem Statement:**

Consider a MOS capacitor structure found in conventional MOSFET devices. The thickness of the oxide region equals 4 nm and the substrate is p-type with doping  $N_{\rm A}$ .

- (a) Assume that N<sub>A</sub>=10<sup>17</sup> cm<sup>-3</sup>. Plot the conduction band profile under equilibrium conditions assuming aluminum gate, n+-polysilicon and p+-polysilicon gate.

- (b) Vary the gate voltage from -2 to 2 V and calculate the high-frequency CV curves using f=1MHz. How does the change in the type of the gate electrode (aluminum vs. n+-polysilicon vs. p+-polysilicon) reflects on the HF CV-curves.

- (c) Assume aluminum gate and plot the HF CV-curves for f=1MHz. How does the change in substrate doping reflects itself on the HF CV-curves. Support your reasoning with a physical model. Assume that  $N_A$ =10<sup>16</sup>, 10<sup>17</sup> and 10<sup>18</sup> cm<sup>-3</sup>.

nanoHub.org

online simulations and more

Flectrostatic Potential

Flect